ST6 Introduction

.cr st6 To load this cross overlay

If you compare the ST6 MCU with the Motorola 6804 you will find many striking resemblances.

Apart from a different assembler syntax there are a few improvements to be found in the ST6.

The most welcome one is the ability to use lookup tables in ROM memory.

However there is an enormous pitfall between the two MCUs, and that's the opcode bit order which is reversed on the ST6!

Especially the bit order of bit numbers inside instructions is particularly tricky.

There are many different micro controllers built around the ST6 MCU. I'm not going to make a list of all the derivatives that (I think) exist. From the assembler's point of view they mainly differ in the Special Function Register definition, the stack depth, RAM, ROM and EEPROM sizes and the availability of an NMI input.

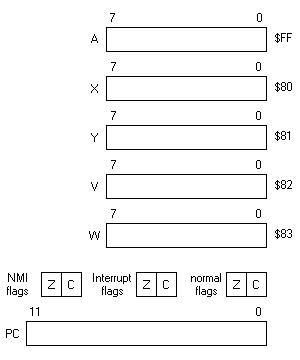

Programming Model

The programming model in the picture below shows the modest register set of the ST6 processor family. I only include a little summary about the features of the ST6's programming model here. It is not my intention to make the original documentation obsolete, so please refer to the original documentation for further details (ST document 2341.pdf).

The ST6 has separate addressing spaces for Program and Data memory. Data address space is only 256 bytes long which allows it to be addressed with only 1 byte. Bank switching is used to extend the addressing range in case there is more RAM available. Data address space does also include a ROM read window, EEPROM memory and Special Function Registers.

The Accumulator A

The Accumulator is used for all arithmetic operations. The Accumulator can also be reached through memory address $FF.

The Index registers X and Y

These registers can be used as 8-bit unsigned indexes to point to any address in Data memory. Because you can read ROM memory through a window mapped in the Data memory area you can now also read from lookup tables, something which could not be done with Motorola's 6804.

The index registers X and Y can also be reached through Data memory addresses $80 and $81 respectively. These memory locations can be addressed with a Short Direct Addressing mode by some instructions.

The registers V and W

The registers V and W can also be reached through Data memory addresses $82 and $83 respectively.

Like the registers X and Y these memory locations can also be addressed with a Short Direct Addressing mode by some instructions.

However they can not be used as index registers like X and Y can!

The Condition Codes

Unlike other micro controllers the ST6 doesn't have a condition code register.

There are only 2 system flags, which are set by most mathematical instructions and can be tested with branch instructions.

Only the Zero and Carry flags are implemented.

Two or three sets of system flags exist, depending on the availability of an NMI input.

The normal set is used during normal operation.

Interrupts will swap these normal flags with the interrupt or NMI flag set.

The RETI instruction will swap the original flags back into place.

This way the flags don't have to be saved on the stack during interrupts.

After a reset the processor will use the NMI flag set (or the interrupt flag set if NMI is not implemented). This is to prevent interrupts while the system is initializing itself. After initialization the program should execute a RETI instruction to enable interrupts which also swaps in the normal system flags.

The Program Counter

The program counter PC is normally incremented after fetching each instruction or operand byte during program execution.

The only way you can change this behaviour is with the jump, subroutine and return instructions.

Interrupts can also change the program counter's value.

The program counter is only 12 bits wide, limiting the program memory to 4k.

Bank switching is used on devices with more ROM memory.

Please note that the stack pointer is not included in the programming model.

The stack of the ST6 consists of 4 or 6 dedicated 12 bit memory locations, not directly addressable in any other way.

Also the stack pointer itself is not accessible.

The only way to manipulate the stack is by using the CALL, RET, RETI instructions and by interrupts.

The stack will overflow if subroutines (and interrupt) are nested too deep.

Executing a RET or RETI instruction when the stack is empty has no effect on the program counter.

The MCU will simply execute the instruction following the ignored RET or RETI instruction next.

Timing

SB-Assembler Version 3 can show you the cycle times of each instruction when the TON list flag is switched on. The numbers presented are the number of clock cycles each instruction takes.

Reserved Words

The SB-Assembler ST6 cross overlay family has just a few reserved words.

You better don't use these words as label names to avoid unpredictable behaviour by the assembler.

The reserved words are: A, X, Y, V and W.

For the rest you may choose any label name you like.

Special Features

Originally the ST6 assembler does not require any prefixes for immediate operands.

This is also true for the SB-Assembler.

In case no prefix is given the low byte of the expression is used as operand.

The SB-Assembler does still allow a prefix to be used in combination with an immediate operand.

This can be useful in case you need some other byte from a 32-bit expression.

Legal prefixes are #, /, = and \.

Overlay Initialization

Two things are set while initializing the ST6 overlay family every time it is loaded by the .CR directive.

- Big endian model is selected for the .DA and .DL directives.

This means that words or long words are stored with their high byte first.

I chose big endian to make the behaviour compatible with the Motorola devices. Since the ST6 is not aware of any 16 bit values, there was no real other guide to select between the two models. - The maximum program counter value is set to $1FFF.

Differences Between Other Assemblers

There are some differences between the SB-Assembler and other assemblers for the ST6 family of processors. These differences require you to adapt existing source files before they can be assembled by the SB-Assembler. This is not too difficult though, and is the (small) price you have to pay for having a very universal cross assembler.

- The obvious differences in notation of directives and radixes common to all SB-Assembler crosses.

- Don't forget that the SB-Assembler does not allow spaces in or between operands. Only Version 3 will allow one space after each comma separating operands in the operand field.