6804 Introduction

.cr 6804 To load the 6804 cross overlay

.cr 68hc04 To load the 68HC04 cross overlay

My guess is that the Motorola 6804 family of micro controllers were Motorola's first steps on the micro controller market.

It is very hard to find information about these controllers on the internet, so my best guess is that the 6804 family has become obsolete.

The family has been extended by some HC members, which basically have slightly different memory sizes and peripheral capabilities.

Further more the 68HC04 series of controllers have 2 extra instructions to enter 2 different low power modes.

The 6804 has some remarkable limitations compared to modern 8-bit micro controllers.

E.g. it can't read from ROM based data tables.

They do have some 60 or 70 bytes of ROM in the data memory map though, so really small lookup tables are possible.

The major disadvantage of these processors is that they are basically all mask ROMmed.

I don't know if any EEPROM versions of these controllers exist.

Programming Model

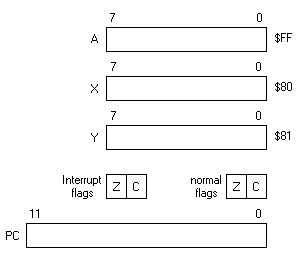

The programming model in the picture below shows the modest register set of the 6804 processor family. I only include a little summary about the features of the 6804's programming model here. It is not my intention to make the original documentation obsolete, so please refer to the original documentation for further details (if you can find any) .

The 6804 is equipped with a Direct addressing mode, like most other processors from Motorola.

In fact the 6804 can't read or write data in other memory pages than page 0.

This automatically means that all I/O must be located in page 0 as well.

Four of the RAM addresses can be addressed with the Short Direct addressing mode.

Short Direct addressing mode can access the memory locations $80, $81, $82 and $83 with only a 2 bit address.

The Accumulator A

The Accumulator is used for all arithmetic operations. The Accumulator can also be reached through memory address $FF.

The Index registers X and Y

These registers can be used as 8-bit unsigned indexes to point to any of the page 0 addresses. Since the index registers are 8-bit wide there is no way to point to ROM address space, so it is not possible to implement lookup tables in ROM.

The index registers X and Y can also be reached through memory addresses $80 and $81 respectively. These memory locations can be addressed with Short Direct addressing mode by some instructions.

Please note that the syntax of the Indirect addressing mode is very important, as you can see in the example below.

LDA ,X Load A with value from address X

LDA X Copy value in X to A

The Condition Codes

Unlike other micro controllers the 6804 doesn't have a condition code register.

There are only 2 system flags, which are set by most mathematical instructions and can be tested with branch instructions.

Only the Zero and Carry flags are implemented.

Two sets of system flags exist.

The normal set is used during normal operation.

Interrupts will swap these normal flags with the interrupt flag set.

The RETI instruction will swap the original flags back into place.

This way the flags don't have to be saved on the stack during interrupts.

The Program Counter

The program counter PC is normally incremented after fetching each instruction or operand byte during program execution.

The only way you can change this behaviour is with the jump, subroutine and return instructions.

Also interrupts can change the program counter's value.

The program counter is only 12 bits wide, limiting the program memory to 4k.

Please note that the stack pointer is not included in the programming model.

The stack of the 6804 consists of 4 dedicated 12 bit memory locations, not directly addressable in any other way.

Also the stack pointer is not accessible.

The only way to manipulate the stack is by using the JSR, RET, RETI instructions and by interrupts.

The stack will overflow if subroutines (and interrupt) are nested more than 4 levels deep.

Timing

SB-Assembler Version 3 can show you the cycle times of each instruction when the TON list flag is switched on. The numbers presented are the number of clock pulses the processor needs to execute the instruction.

Reserved Words

The SB-Assembler 6804 cross overlay family has just a few reserved words.

You better don't use these words as label names to avoid unpredictable behaviour by the assembler.

The reserved words are: A, X and Y.

For the rest you may choose any label name you like.

Special Features

Compound instructions

Motorola has proposed some compound instructions, which are all implemented in the SB-Assembler 6804 cross overlay.

Please refer to the file 6804.asm in the opcode.tst directory for a complete list of these instructions.

Compound instructions usually use the possibility to address the A, X and Y registers from internal memory.

This way we can create new instructions like CLRA (translated to SUB $FF) and INCX (translated to INC $80).

Indirect addressing mode

Please pay some attention to the syntax for Indirect addressing mode. Indirect addressing mode uses the contents of the X or Y register to point to one of the page zero addresses. The syntax for this addressing mode is:

LDA ,X Two examples of Indirect addressing mode

ADD ,Y Please note the comma in front of X and Y

Omitting the comma in front of the index register will result in using Direct addressing mode instead of Indirect addressing mode. The instruction LDA X will therefore copy the contents from register X to to A.

Forced Short Direct page

Data memory references are normally 8-bits wide and are called Direct addressing mode. Four bytes in this 256 bytes long address space are addressable with only 2 bits, which is called Short Direct addressing mode. These are the addresses $80, $81, $82 and $83. Please note that the X and Y registers are also located there.

Usually the SB-Assembler will automatically select the most economical addressing mode. This means that Short Direct addressing mode is always selected when possible. The expression identifying the address must be resolved completely before we can know for sure if the address is a Short Direct address. Normal Direct addressing mode is selected if the expression contains any forward referenced labels.

You may override this automatic selection of addressing mode by preceding the address field with a < or a > symbol.

The < symbol forces the assembler to use Short Direct addressing mode, even if the address expression contains a forward referenced label.

On the other hand the > symbol will force the assembler to use the Direct addressing mode, even if the address could be resolved to a Short Direct address.

But a Out of range error will be reported if you try to force to use the Short Direct addressing mode on other addresses than $80, $81, $82 or $83.

Bit Branch operand syntax

The SB-Assembler uses a small difference in syntax for the bit test and branch instructions compared to the Motorola rules.

Motorola separates the Direct address and the destination address in the operand field by a space.

The SB-Assembler doesn't allow spaces in the operand field.

You should use commas to separate the operands in the operand field at all times.

This means that you simply must replace Motorola's space by a comma.

Overlay Initialization

Two things are set while initializing the 6804 overlay family every time it is loaded by the .CR directive.

- Big endian model is selected for the .DA and .DL directives. This means that words or long words are stored with their high byte first.

- The maximum program counter value is set to $1FFF.

Differences Between Other Assemblers

There are some differences between the SB-Assembler and other assemblers for the 6804 family of processors. These differences require you to adapt existing source files before they can be assembled by the SB-Assembler. This is not too difficult though, and is the (small) price you have to pay for having a very universal cross assembler.

- Not all assemblers will understand forced Short Direct and forced Direct addressing modes.

- Not all assemblers will understand the compound instructions.

- Bit Test And Branch operand syntax is slightly different from Motorola's original syntax.

- The obvious differences in notation of directives and radixes common to all SB-Assembler crosses.

- Don't forget that the SB-Assembler does not allow spaces in or between operands. Only Version 3 will allow one space after each comma separating operands in the operand field.